*******************************************************************

ビッグデータ時代を迎え、全世界のデータ量は 10 年後に 100 ゼタバイト zetta-byte (100×1021バイト) に達すると予測されている。地球上の浜の真砂の概算数は 10 ゼタバイト程度で、これを遥かに上まわる。同時にメモリの消費電力も飛躍的に増加して、ある試算例では、このままでは 2025 年に 50 GW、原発 50 基分にもなるという。半導体メモリの選択基準 figure-of-merit も、今までは集積度と読み書き速度であったが,モバイルやウェアラブル機器の電池切れの問題もあって,ビット当たり消費電力が注目されている。

日本の半導体産業の衰退に伴って,マスメディアは技術動向への関心を失っているが,産業全体へのインパクトが巨大であることには変わりはない。

開発中のものを含め,おもな書き換え可能な半導体メモリを整理すると;

① 揮発性メモリ volatile memory

回路に (1,0) の二つの状態を作り記憶する。電源を切ると記憶が消える。

- スタチック回路 ・・・ SRAM: Static Random Access Memory

- ダイナミック回路 ・・ DRAM: Dynamic Random Access Memory

スタチック回路は,普通の電子回路である。ダイナミック回路は、動作時に電源ラインまたはグランドのいずれにも接続されないフロート状態になる節点を設けて、そこに電荷を保持するもの。回路規模を縮小できるが、電荷は次第に散逸するので、再補充 refresh のための dynamic 動作が必要である。

② 不揮発性メモリ non-volatile memory

- 電極や導体に (1,0) の状態を刻印する。電源を切っても消えない。

- 電極の帯電状態で(1,0)を記憶=NAND型Flash-Memoryなど

- 電極の帯磁状態で(1,0)を記憶=MRAM(Magneto-resistive RAM)など

- 導体の抵抗変化で(1,0)を記憶=ReRAM(Resistance RAM)など (RRAMはシャープの登録商標なので、一般にはReRAMを使う)

半導体 LSI の集積度について考えると, Design Rule を特徴付けるのは,最小加工寸法の feature size : F (通常はゲート長、単位: nm) である。また、基本回路cellが最小単位の F の自乗 = F2 の何倍の面積になるかの指標を cell area factor と言う。微細化とともに、大容量メモリの重要な選定基準である。SRAM のセルエリアファクタは 100 程度にもなり、CPU と高速でデータをやり取りするキャッシュメモリ cache memory 以外には、あまり使われない。

NAND 型 Flash-Memory はメモリ領域と隣接スペースにそれぞれF、合計で 2F になるので 2F×2F=4F2 と、面積を最小にできる。また、溶融石英 SiO2 という理想的な絶縁材料の中の電極に電荷を書き込んでいるので,帯電は 10 年以上も保持される。このためデータ保持の消費電力は極めて少ないが,書き込み速度が遅く,書き換え回数にも制限があり(~105),バックアップ用途でしか使えない。また、最近になってデバイス設計上の限界も見えてきた。

一方メインメモリに使われている DRAM は高速で書き込みでき,NAND に次いで集積度が高いが(6F2 から 4F2 に縮小化途上),回路の中のキャパシタにデータを充電させるという動作原理から、データ保持時間 retention time が 100 ms 以下と短く定期的な再書き込み refresh が必要である。このため消費電力をなかなか下げられない。

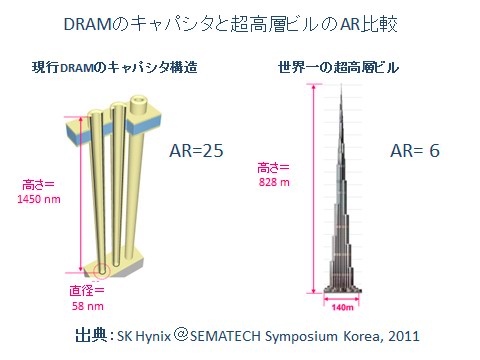

DRAM のデータ保持用のキャパシタは,限られたスペース内で静電容量を稼ぐために円筒形状にして、狭隘な都市部の高層ビル群のように林立させ、ひたすら背を高く伸ばしてきた。次世代では,アスペクト比 Aspect Ratio (AR ≡高さ/底面寸法)が 100 に達し、微細化も限界になる。ちなみに、東京タワーは AR =3.5、スカイツリーは AR = 9.3,超高層ビルも 6 以下である(下図)。

要するに,DRAM と NAND という情報通信を支える2大メモリの賞味期限が切れようとしている。もちろん,過去にも似たような限界論が繰り返され,また狼少年だよと様子見をする人も多い。イチローや Legend 葛西のように限界説を乗り越えて活躍する現役も多く、侮れないのは事実であるが・・・。

DRAM と NAND は,回路や電極に電荷が有れば 1、無ければ 0 という形で記憶する電荷蓄積型メモリである。この原理に限界が出てきたので,次世代のメモリは,磁化極性や抵抗値の変化で記憶するタイプに移行する。

電流を流して磁化を反転させ記憶するのが,MRAM である。巨大な磁気抵抗変化にはいろいろな原理があるが,最先端の STT-MRAM (Spin Transfer Torque MRAM) は電子のスピンに (1,0) を刻印する(spintronics)。外乱磁界がなければ,NAND 同様に 10 年以上のデータの保持が可能である。書き換え回数も,DRAM 同様に気にしないでよい。素材を磁化して書き込むので,書き込み電流の漏れ磁場の影響を防ぐためには,隣接セルとの距離を離す必要があり,現状ではセル面積を ~ 6F2 以下にできないようだ。多層化や,一つのメモリセルに複数ビットを記憶させる多値化も難しいようだ。

電圧を印加したときの抵抗変化を利用して記憶するのが,ReRAM である。NAND と同様に,10 年以上のデータの保持が可能である。巨大な抵抗変化にはいろいろなタイプがあり,材料も多種多様である。たとえば酸化物半導体に電圧を印加することにより,電子伝導性のある酸素空孔の数を増減させて抵抗値を変化できる。電流を流した時の磁場と異なり,電圧印加時の電界の漏れは小さいので,隣接セルとの距離を離す必要がなく,セル面積を最小寸法の 4F2 に近づけることができる。DRAM のプロセスとの整合が良く,多層化できること,電気抵抗の変化率が数十倍もあるので、多値化も可能であることも強みとされる。書き換え回数がまだ短い(~106)のが最大の課題である。

昨年12月のコラムで memristor を紹介した。開発者の Leon Chua 教授と HP は,すべての ReRAMはmemristor の一種であると主張している。異論反論も多く,ご本家争いが続いているようである。将来の高速・不揮発・大容量の三位一体のユニバーサルメモリを目指し、開発競争が当面続く。

さて万能細胞から人間の脳が作れるとして(iPS 細胞で部分実証済み)、記憶装置として使えるだろうか。大脳の記憶容量には諸説あるが約 10 テラバイト tera-byte(10×1012バイト)、消費電力を約 20 W とする。これで将来の 100 ゼタバイトのメモリ需要を満たすと、原発 200 基分の電力が必要となる。検索速度や機能も劣り、稗田阿礼型バイオメモリは魅力がなさそうだ。